ジェンスン・フアンは「ムーアの法則は死んだ」と言う、まだそうとは言えない[英エコノミスト]

![ジェンスン・フアンは「ムーアの法則は死んだ」と言う、まだそうとは言えない[英エコノミスト]](/content/images/size/w1200/2023/12/getty-images-B3Dxa-OBzyk-unsplash.jpg)

60歳の誕生日を2年後に控えたムーアの法則は、理論物理学者エルヴィン・シュレーディンガーの仮説上の猫のように、死んでいるようで生きている。1965年、インテルの共同創業者の一人であるゴードン・ムーアは、マイクロチップに詰め込める電子部品の一種であるトランジスタの数が12ヵ月ごとに倍増していることを観測した。

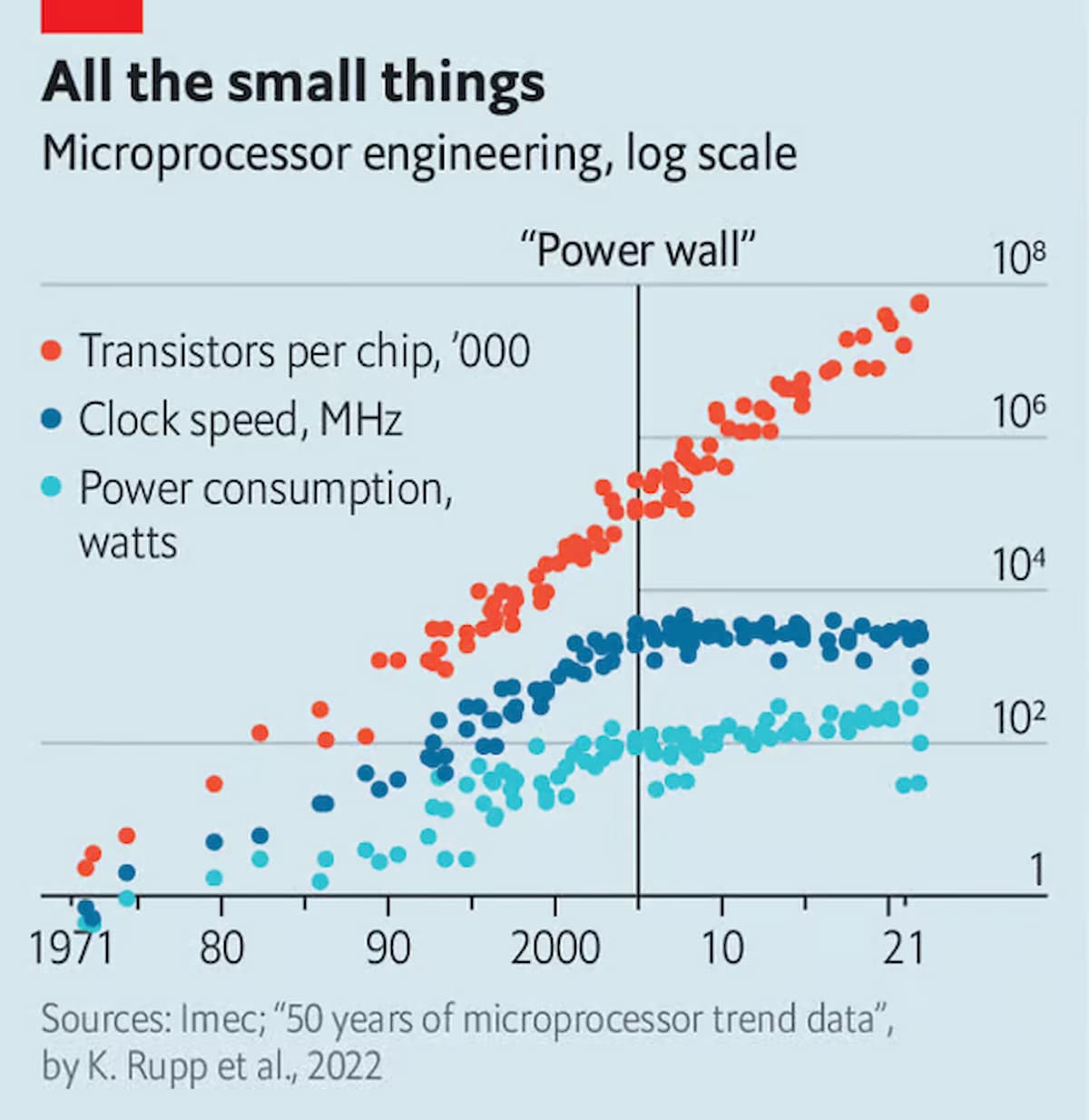

この観測は、コンピューティング業界全体のペースを決める願望となった。1971年に製造されたチップは、1平方ミリメートルに200個のトランジスタを搭載できた。今日の最先端チップは、同じスペースに1億3,000万ものトランジスタを詰め込み、しかもそれぞれ数万倍も高速に動作する。もし自動車が同じ速度で改良されていたら、現代の自動車の最高速度は時速数千万マイルに達していただろう。

ムーアは、このプロセスが永遠に続くわけではないことをよく知っていた。倍増するたびに、前より難しく、より高価になるのだ。2022年9月、チップメーカー、エヌビディアのボス、ジェンスン・フアンは、ムーアの法則は「死んだ」と宣言し、時を告げる最新のオブザーバーとなった。しかし、誰もが同意しているわけではない。数日後、インテルのパット・ゲルシンガー最高経営責任者は、ムーアの法則は実際に「健在」であると報告した。

サンフランシスコで毎年開催されるチップ業界の展示会、国際電子デバイス会議(IEEE International Electron Device Meeting; IEDM)の参加者は、ほとんどゲルシンガーの味方だった。研究者たちは、ムーアの法則を維持するために、3次元の利用からチップのサンドイッチ化、さらには過去半世紀にわたってマイクロチップの材料として使われてきたシリコンを超えるものまで、さまざまなアイデアを披露した。

トランジスタは、電気にとっての水道のようなものだ。電流はトランジスタのソースからゲート(トランジスタのオン・オフを切り替えるスイッチ)を介してドレインに流れる。ゲートに電圧がかかると、電流はオンになる。この1と0から、気候モデルやChatGPTからTinderや『グランド・セフト・オート』まで、あらゆるコンピュータ・プログラムが構築されている。

小さいことは美しい

何十年もの間、トランジスタは、ソースとドレインをつなぐシリコンのチャネルの上にゲートがある、ほとんど平坦な構造として作られてきた。トランジスタを小さくすることは、歓迎すべき副次的な利点をもたらした。より小さなトランジスタは、より素早くオン/オフでき、そのために必要な電力も少なくて済んだ。

デナード・スケーリング(デナード則)として知られる現象だ。しかし2000年代半ばまでに、デナード則は終焉を迎えた。トランジスタのソースとドレイン間の距離が縮まると、量子効果によってゲートがチャネルの制御を失い始め、トランジスタがオフのつもりでも電子が移動してしまう。このリークは電力を浪費し、簡単に処分できない余分な熱を発生させる。この「電力の壁」に直面し、トランジスタ数が増加し続けているにもかかわらず、チップ速度は停滞している(グラフ参照)。

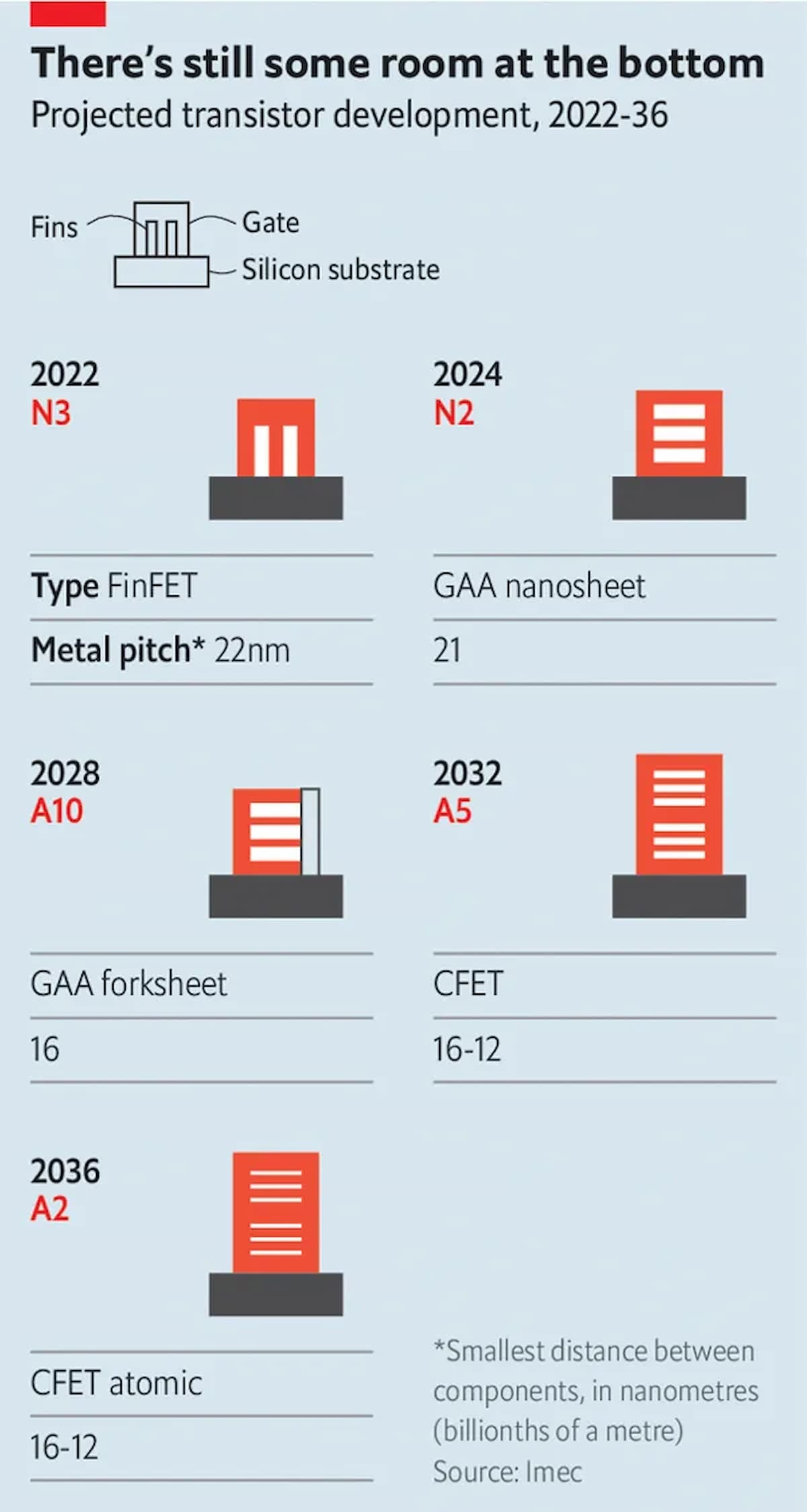

2012年、インテルはチップを3次元で作り始めた。平らな導電チャネルを表面から突き出たフィンに変えたのだ。これにより、ゲートがチャネルの3面を取り囲むようになり、再び制御できるようになった(グラフ参照)。「FinFET(フィンフェット)」と呼ばれるこのトランジスタは、リーク電流が少なく、スイッチング速度が3分の1速く、消費電力は前世代の約半分である。しかし、このフィンをより薄く、より高くするには限界があり、チップメーカーは現在それに近づいている。

次のステップは、ゲートがフィンを完全に取り囲むようにフィンを横向きにし、最大限に制御することだ。韓国の電子機器大手サムスンは、「ナノシート」と呼ばれるこのようなトランジスタをすでに最新製品に採用している。インテルや台湾のチップファウンドリーであるTSMCも間もなくこれに続くと見られている。複数のシートを重ねて長さを短くすることで、トランジスタのサイズをさらに30%小さくすることができる。

TSMCの研究者であるSzuya Liaoは、3D化を都市の高密度化、つまり広大な郊外を超高層ビルに置き換えることに例えている。また、高さが増しているのはトランジスタだけではない。チップはトランジスタを論理ゲートにグループ化し、初歩的な論理演算を実行する。最も単純なものはインバーターだ。論理ゲートは、N型とP型と呼ばれる2つの異なるタイプのトランジスタを組み合わせることによって作られる。インバーターには、それぞれ1つずつが必要で、通常は並べて配置される。

IEDMでLiaoと同僚たちは、その代わりに互いに積み重ねられたトランジスタから作られたコンプリメンタリFET(CFET)と呼ばれるインバーターを披露した。TSMCによれば、3Dにすることで絶縁層を追加するスペースができ、インバーター内のトランジスタの電流漏れが少なくなるため、エネルギーの無駄遣いが減り、発熱量も少なくなるという。

3Dチップ製造の究極の発展は、チップ全体を積み重ねることである。最新のプロセッサーの性能に対する大きな制限のひとつは、コンピューター内の他の場所にあるメモリー・チップから、どれだけ速くデータを受け取って処理できるかということだ。マシンの中でデータを移動させるには多くのエネルギーを消費し、数十ナノ秒(※ナノ秒は10億分の1秒)というコンピュータにとっては長い時間がかかる。

ベルギーのチップ研究機関であるIMECの研究者、ジュリアン・リッカートは、3次元積層がどのように役立つかを説明した。データ処理に必要なメモリチップの間にメモリチップを挟むことで、データを必要な場所に送るのに必要な時間とエネルギーを大幅に削減できる。2022年、TSMCが製品を製造しているアメリカのAMDは、3Dテクノロジーを使ってプロセッサの上に直接大きなメモリの塊を貼り付ける「X3D」製品を発表した。

しかし、都市と同様、密度は混雑を意味する。マイクロチップは複雑な電気回路で、円形のシリコン・ウェハーの上に下から順番に作られる(インテルはこれをピザ作りに例えている)。まずトランジスタが作られる。その上に、電力と信号を伝送する金属ワイヤーが何層にも重ねられている。最近のチップには、このようなワイヤーが15層以上ある場合もある。

チップが高密度になるにつれて、電力線とデータバスの配線は難しくなる。迂回ルートはエネルギーを浪費し、電力線はデータバスに干渉する可能性がある。3次元論理ゲートは、一定の面積にさらに多くのトランジスタを詰め込むため、事態をさらに悪化させる。

この混乱を解消するため、チップメーカーは「バックサイド・パワー・デリバリー(裏面電源供給)」と呼ばれるアプローチで、電力線をトランジスタの下に移動させている。トランジスタとデータバスは以前と同じように作られる。その後、ウェハーを反転させ、太い電源線を下に追加する。電源線をチップの下面に沿わせることは、高価なチップ工場の運営方法を根本的に変えることを意味する。しかし、電力線の長さを短くすることは、無駄なエネルギーを減らし、より低温で動作するチップを意味する。また、トランジスタ上部の面積が5分の1近く空くため、設計者はデータバスを追加する余裕ができる。最終的には、トランジスタのサイズを変更することなく、より高速で電力効率の高いデバイスが実現する。インテルは来年からチップに裏面電源供給を使用する予定だが、3次元トランジスタと組み合わせて本格的に生産するのはまだ先のことだ。

余分な次元を利用することにも限界がある。トランジスタのゲート長が10ナノメートルに近づくと、それが支配するチャネルは約4ナノメートルより細くする必要がある。このような極小サイズ(わずか原子数十個分)では、リーク電流(漏れ電流)が非常に悪化する。シリコンの表面粗さ(仕上がり面の凹凸の程度)が電子の動きを妨げるため、電子の速度が遅くなり、トランジスタのスイッチのオン・オフがうまくいかなくなるのだ。

そこで一部の研究者は、コンピュータ時代を築いてきたシリコンを捨てて、遷移金属ジカルコゲナイド(TMD)と呼ばれる新しいクラスの材料を使うというアイデアを研究している。TMDは、わずか3原子厚のシート状にすることができる。その多くは、ごく小さなトランジスタからの電流リークが少ないという電気的特性を持っている。

特に有望視されているのは、二硫化モリブデン、二硫化タングステン、二セレン化タングステンである。しかし、シリコンは60年の経験を持つが、TMDはあまり理解されていない。技術者たちはすでに、その極薄のプロファイルが、それで作られたトランジスタをチップの金属層と接続することを難しくしていることを発見している。また、特に信頼性の高い大量生産に必要な規模での一貫生産も難しい。また、この材料の化学的特性は、N型とP型のトランジスタを製造するためのドーピング(結晶の物性を変化させるために少量の不純物を添加)が難しいことを意味する。

原子時代

これらの問題は、おそらく克服できないものではない。(シリコンは業界の初期にドーピングの問題に悩まされた)。IEDMでは、インテルがTMDで作られたインバーターを披露していた。しかし、スタンフォード大学の電気エンジニアであるエリック・ポップは、商用製品でシリコンが使われなくなるのはまだ先のことだと考えている。ほとんどの用途では、シリコンはまだ「十分」だと彼は言う。

ある時点で、どんなに巧妙な技術を駆使しても、トランジスタをこれ以上縮小できない日が来るだろう(例えば、原子1個分以下の材料でトランジスタを作ることは難しい)。ムーア自身が2003年に警告したように、「指数関数に永遠はない」。しかし、彼は集まったエンジニアたちに、「あなたの仕事は終わりを永遠に遅らせることだ」と言った。チップメーカーは、ムーアの講演以来20年間、それを見事に実践してきた。そして、少なくとも次の20年に向けての道筋も描いている。■

From "Jensen Huang says Moore’s law is dead. Not quite yet", published under licence. The original content, in English, can be found on https://www.economist.com/science-and-technology/2023/12/13/jensen-huang-says-moores-law-is-dead-not-quite-yet

©2023 The Economist Newspaper Limited. All rights reserved.

翻訳:吉田拓史