Appleの新チップはTSMCの優位性を再確認させる

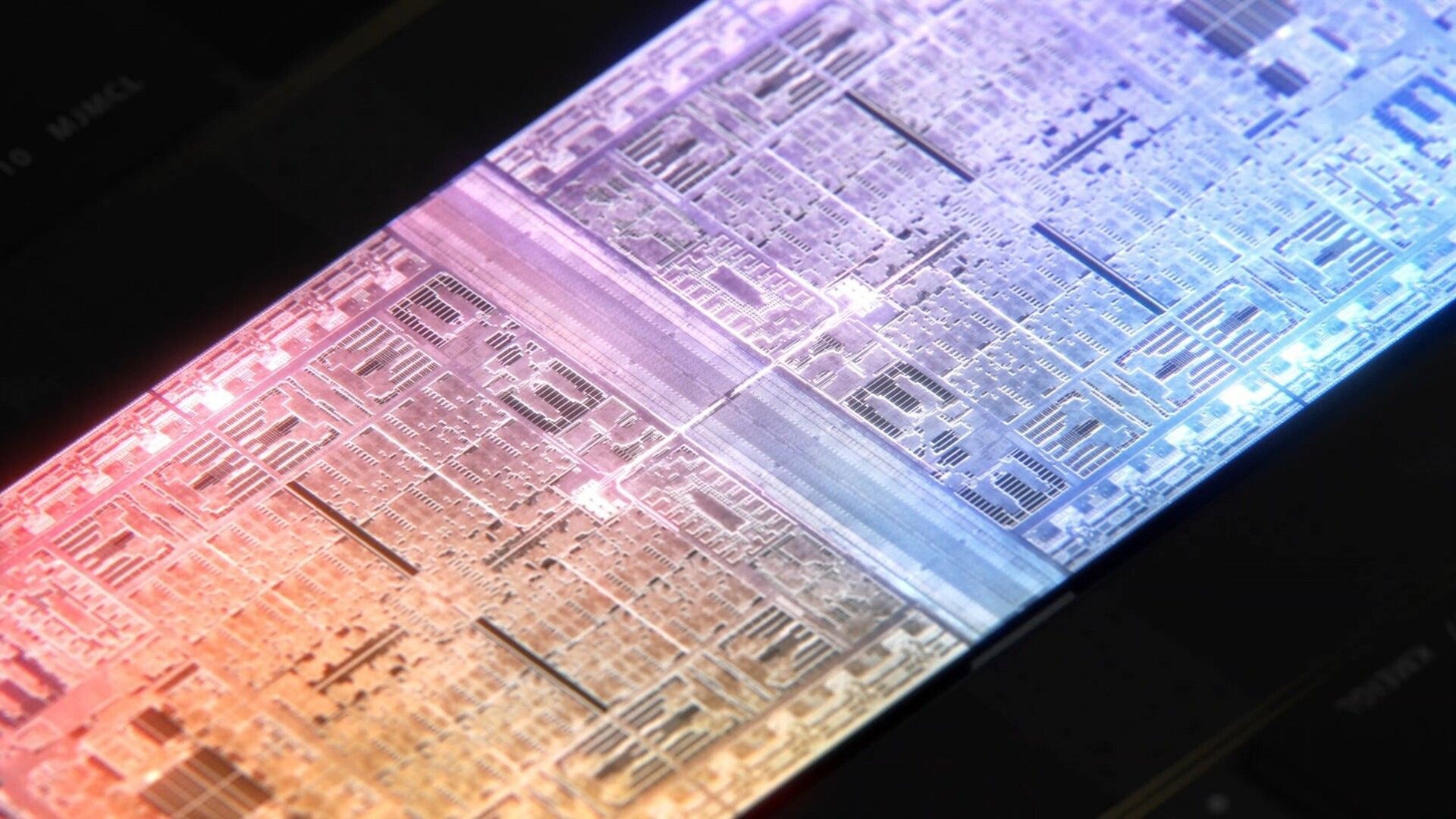

3月初旬にアップルの最新コンピュータ「Mac Studio」の心臓部に搭載されたM1 Ultraは、TSMCの技術がいかに競合他社に差をつけているかを印象づけた。

Appleは3月初旬に最新コンピュータ「Mac Studio」を発表した。話題の中心となったのは、その心臓部に搭載された強力なチップだった。そしてそのチップはAppleがいかにTSMCの技術に依存しているかを端的に示している。

M1 Ultraは、デスクトップをターゲットにしており、CPUとGPUの両方のワークロードに対して、システムオンチップ(SoC)の性能を再び向上させた。

新しいM1 Ultraの核となるのは、少し前のM1 Maxだ。具体的には、Appleはここで2つのM1 Maxダイを使用し、それらを結合して1,140億のトランジスタの集積体を形成している。

M1 Max自体は5ヶ月間以上前から出荷されており、チップの基本的なアーキテクチャ(とその基礎となるブロック)は、この時点で既知のものだ。M1 Ultraは、エンドユーザー向けの機能で新しいものを導入するのではなく、1つのチップに2つ目のシリコンダイを載せることで、AppleのM1アーキテクチャをさらに一歩スケールアップさせた。

2つのチップを組み合わせることで、AppleのM1 Ultraは、20個のプロセッシングコアと64個のグラフィックスコアを構成する1,140億個のトランジスタを実現しました。これに対し、AMD Ryzenデスクトップ・プロセッサーのトランジスタ数は、その10分の1程度だ。

M1 Ultraは、複数のGPUを十分な内部帯域幅を実現できるほどの膨大なダイ間帯域幅でリンクさせるという10年以上にわたって複数の企業が取り組んできた懸案をクリアしたと考えられるとAnandTechのRyan Smithは記述している。

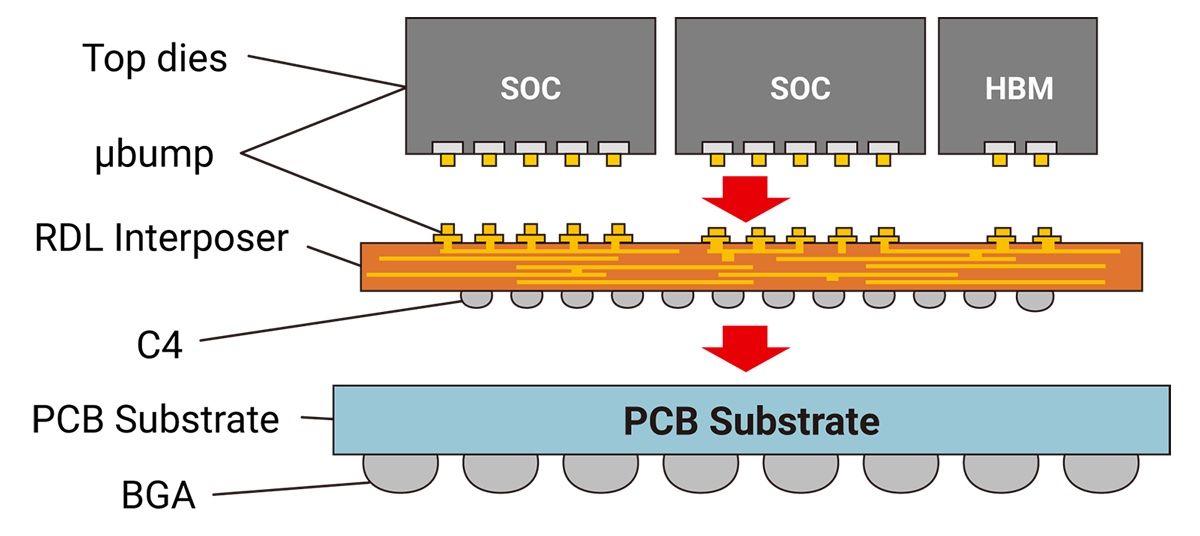

Appleは「隠し味」としてM1 Maxの片方のエッジに非常に高速なインターフェイスを搭載している。このインターフェースは、シリコンインターポーザーの助けを借りて、2つのM1 Maxのダイを連結させることができる。

AppleはこのパッケージングアーキテクチャをUltraFusionと呼んでおり、2.5Dチップパッケージングの業界における最新の例となっている。「詳細は実装ごとに大きく異なるが、この技術の基本は同じだ。いずれの場合も、2つのチップの下に何らかのシリコンインターポーザーを配置し、2つのチップ間の信号をインターポーザーを介して配線する。シリコンの超微細な製造能力は、2つのチップの間に膨大な数のトレース(Appleの場合は1万本以上)を配線できることを意味し、これにより2つのチップ間の超広帯域、超高帯域の接続が可能になるのである」とRyanは書いている。

UltraFusionを使うことで、Appleは2つのM1 Maxのダイ間で2.5TB/秒という驚異的な帯域幅を提供することができる。この高速性は、一方のチップのコアが、もう一方のチップに接続されたメモリに到達するために必要なものだ。特にグラフィック・プロセッシング・ユニットは、メモリに保存されたデータを貪欲に利用する。

インターポーザーはこれまで、大型で高価なものでした。Appleのカスタムアプローチは、M1 Maxチップの接続エッジを横切るだけの微細なスライスを含んでいる。

DigiTimesは、AppleのM1 Ultraプロセッサは、TSMCの2.5D(2.5次元)シリコンインターポーザーを使用したパッケージングプロセスであるCoWoS-Sを使用して作られたと報じている。同様の技術は、AMD、Nvidia、富士通などの企業が、データセンターやハイパフォーマンスコンピューティング(HPC)向けの高性能プロセッサを製造する際に使用している。

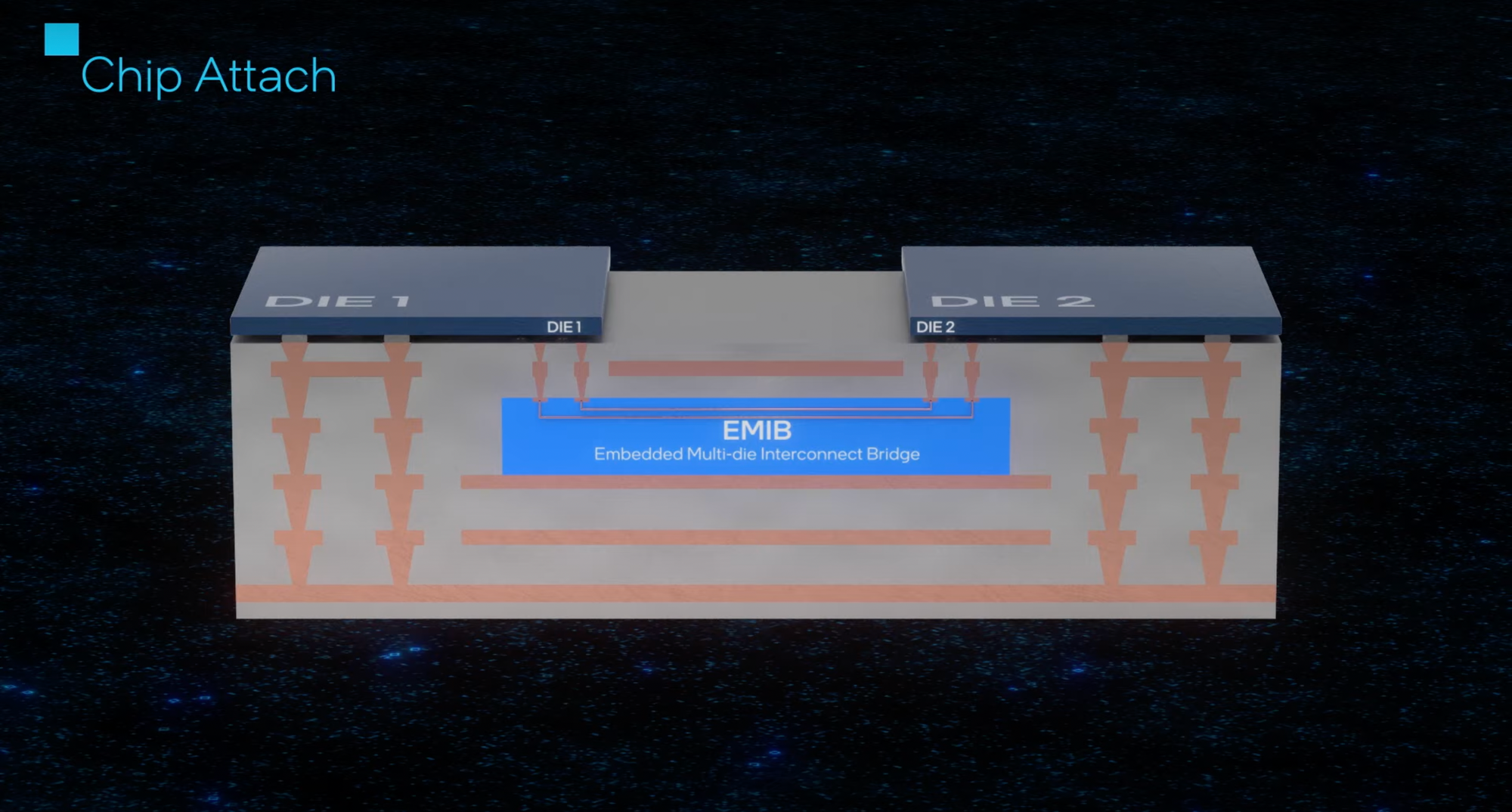

チップをつなぐ先進的なパッケージング技術に取り組んでいるのは、Appleだけではない。 Intel、AMD、Nvidiaも、ダイまたはチップレットと呼ばれる複数のチップ素子を組み合わせて、より大きな一つのプロセッサにする技術を持っている。M1 Ultraは、これまでのところ、間違いなくこのコンセプトの最も進んだ例だが、競合が追いついてくることは必定だ。

Intelは同様のパッケージング技術を開発し、Embedded Multi-Die Interconnect Bridge(EMIB)と呼んでいる。インテル社は、まだ市場に出ているチップにEMIBを使用していないが、今年後半には、コードネーム「Sapphire Rapids」と呼ばれるハイエンドサーバーチップの販売を開始する予定である。Sapphire Rapidsは、4つのチップと4つの大きなメモリモジュールをリンクさせるためにもEMIBを使う予定だ。

Real World TechnologiesのアナリストであるDavid Kanterは、UltraFusionのより高価で高密度のワイヤにより、Appleは1つのチップから別のチップにデータを送る速度が、Sapphire Rapidsを使用するIntelのおよそ2倍であると述べている。

またKanterは、TSMCの新技術がインテルのものとコスト面でどのように比較されるのか、まだ確かなデータはないと注意を促している。先進的なパッケージング技術には非常に多くの異なる技術的詳細があるため、インテルとTSMCの間で正面から競争するというよりも、チップ設計者が自分たちの目標に合ったものを選ぶということがよくあると、バードマンは述べている。

DigiTimesは、Appleが必要とする品質と量を提供できるABF(味の素ビルドアップフィルム)基板のサプライヤーは、現在台湾のユニミクロン・テクノロジー(欣興電子)だけであることも報じた。

ユニミクロンは昨年末、2022年の資本支出を当初予定の297億3000万台湾ドル(約1,250億円)から358億5800万台湾ドルに拡大し、主にABF基板の能力拡張を支援すると発表した。これはAppleの需要を見越した能力増加だろうか。