RISC-VがArmに取って代わる 命令セットオープン化の衝撃

RISC-VはARMの牙城を崩しかねない。チップデザイナーは、CPUの性能改善の速度が遅くなったいま、アプリケーション固有のプロセッサを作成して速度の低下を補うように圧力を受けている。RISC-Vコミュニティが提示する「ISAのオープンソース化」は、ARMのIPビジネスモデルに疑問を投げかけている。

要点

RISC-VはARMの牙城を崩しかねない。チップデザイナーは、CPUの性能改善の速度が遅くなったいま、アプリケーション固有のプロセッサを作成して速度の低下を補うように圧力を受けている。RISC-Vコミュニティが提示する「ISAのオープンソース化」は、ARMのIPビジネスモデルに疑問を投げかけている。

ARMのIPビジネスへの不満

ARMは、世界で最も成功したマイクロプロセッサアーキテクチャのひとつであり、ライセンスを取得した半導体会社は年間数十億個のチップを出荷しています。

ARMがマイクロプロセッサをIPとして半導体会社にライセンスする方法は、ARMのビジネスの重要な柱です。半導体会社は自分でチップを製造する場合もあれば、外部の半導体製造会社に製造を委託する場合があります。できあがったチップは半導体会社により、携帯電話メーカー、 デジタルカメラなどの機器メーカーに供給されます。

近年、集積回路 (IC) の開発において、「システム・オン・チップ」 (SoC) と「システム・オン・パッケージ」に依存する傾向が強まっており、モジュール化された再利用可能なコンポーネントを1つのSoCに統合するという新しいIC設計アプローチがそれを伴っています。

ARMは顧客に完全な設計ソリューションを提供するためには、複数のIPプロバイダ(ARMを含む)が互いに協力し、必要な補完的な機能や技術を提供するサードパーティと協力しています。サードパーティには、集積回路設計用のソフトウェア、すなわちEDA(Electronic Design Automation)のプロバイダや設計サービスプロバイダが含まれます。前者はIPコンフィギュレーションのためのプラットフォームを提供しているが、後者は、様々な設計サービスや、製造に必要なダウンストリーム活動の調整を含むソリューションを提供する仲介企業と考えることができます。

ARMはこの複雑なエコシステムの中心に位置しています。IC設計の実現は、ARMを含むバリューチェーンの上流で活動する企業が提供する能力と技術に依存していますが、チップ上のシステム(SoC)の物理的な実現は下流で行われ、他のタスク(製造、アセンブリ、テストなど)や、マスクサプライヤ、ファウンドリ、OEM(相手先ブランド品メーカー)などの関係者との協力が必要になります。

業界のアーキテクチャは非常に断片化されているため、ARMは交換パートナーの複雑なネットワークを調整しなければなりません。この調整作業には、パートナーとの間で2つの異なるタイプの課題を管理する必要があります。

ARMの収益源は、ライセンス(使用許諾)とロイヤリティ(知的財産権)が主要なものです。まず、ARMから半導体製造会社へ、その設計図の利用を許可する段階で、契約料としてライセンスを徴収します。さらに、チップが工場で生産・出荷されるたびに、ロイヤリティがARMへもたらされます。数年の研究開発期間の後、ARMが作成した設計図に基づいた半導体は、様々な用途に応用されるため、その知的財産権は25年以上有効だと言われます。その間、ARMは継続的にロイヤリティ収入を得続けます。ARMはIPビジネスを堅実なものとするため、ライセンスの選択肢を提供しています。

半導体会社がARMのCPU IPに基づき、SoC(システムオンチップ)を開発し機器メーカーに売る場合は、20~100倍ぐらいの付加価値が生まれます。ARMのCPU IPの収益は300億円以下なのに比べて、ARMのCPU IPを搭載するチップの売上は何兆円単位になるためです。その差は付加価値の差であるため、ARMより川下のプレイヤーにも収益が行き渡るのです。

ARMは非常に収益性の高いビジネスを展開していますが、裏返せば、そのIPを利用してチップを製造するベンダーにとってはかなり厳しい条件を提示し続けていると言わざるを得ません。特に近年のSoCのライフサイクルは短期化が進行しており、ARMを採用するリスクが拡大しています。

それでも、このIPビジネスを守るため、ARMはかたくなに命令セットアーキテクチャ(ISA)を守ってきました。これらのARMチップのアーキテクチャの設計図とARM ISAのIPの岩盤もまた、ベンダーやエンドユーザーの側から見ると柔軟性に欠けているように見えます。半導体の研究者もまた、このIPの壁のせいで研究に困難を覚えることがありました。それが「RISC-V」と呼ばれるライバルの出現をもたらしたのです。

RISC-Vとは?

RISC-Vは、研究者が始めた「オープンソース」のISAです。ARMやMIPS、x86などに比べて、RISC-Vはオープンな規格であり、誰でも自由に実装できるということを意味します。それ以上に、ややオープンな開発モデルを持っています。これはRISC-Vの進化を管理するために設立された非営利団体「RISC-V Foundation」によって管理されており、Google、Qualcomm、Microsemi、Nvidia、NXP、その他様々な企業がメンバーとして参加しています。

RISC-Vのもう一つの側面は、他のプロプライエタリな命令セットとは異なり、カスタム拡張を可能にし、実際に奨励している点にあります。ARMプロセッサを構築するためにライセンスを購入した場合、BroadcomやQualcomm、Samsungのような企業が持っているようなアーキテクチャライセンスを取得しても、ARM命令セットの独自の実装を行うことができますが、独自のカスタム命令を追加することはできません。これは最終的にはARMが顧客からのフィードバックを得て、将来のISAのリビジョンで新しい命令を追加することになりますが、個々のライセンシーが追加できるものではありません。

もちろん、オフコア用の密結合アクセラレータのためにアクセラレータを取得する方法は他にもありますが、命令セット自体をカスタムで拡張することは制限されています。前述したように、RISC-Vにはオープンな開発プロセスがあります。RISC-Vファンデーションのメンバーでないと開発の議論に参加できないところもあります。これは比較的低コストで、企業の場合は最低でも年間5,000ドル程度、アクティブなオープンソース開発者の場合は無料、それ以外の場合は個人で100ドル程度で参加できます。

RISC-Vの命令セットアーキテクチャ自体については、実際のところ、あまり目新しいものではありません。特に奇抜で面白い設計決定をしているわけではありません。64ビットと32ビットのISA、RISC ISA は何十年も前から存在しており、それらをどのように構築するかについては膨大な知識があります。

RISC-Vの主な目的はスケーラビリティです。RISC-Vは、高性能コンピューティングやラックスケールコンピューティング、MMU を持たない組み込みデバイス、個々のマイクロコントローラよりも小さいユースケースに至るまでスケールアップできるISAを目指しています。これは実際には現実的な問題であり、当初AMDのような企業がRISC-Vに惹かれていました。初期の RISC-V 開発者会議で、AMDの誰かが手を挙げて、彼らが興味を持った理由は、AMDのプロセッサを出荷するときに、最近のプロセッサには15の異なるISAが搭載されていたからだと言ったと言われます。

RISC-Vは、将来を見据えて設計されたオープンスタンダードであり、レガシーな要素をできる限り排除しています。例えば、RISC-Vのダイナミックワイドベクトル命令セットは、任意のサイズのデータに対してベクトル命令を最大の効率で実行することを可能にします。

例えば、SSEとSSE2はPentium IIIの128ビットレジスタを使用できますが、i7-4770の256ビットレジスタをフルに活用するには、同じ数学演算を行うために全く別の命令セット(AVX2)が必要です。また、i7-1065G7の512ビットレジスタを利用するには、同じ演算を行うためにAVX-512という別の命令セットが必要になります。

一方、RISC-Vベクトル演算では、現在のCPU設計で利用可能なあらゆるサイズのレジスタを使用して、1つのCPU命令セットで同じ数学的演算を可能な限り効率的に実行できます。つまり、開発者は、64ビットのレジスタを持つ携帯電話でも、1024ビットのレジスタを持つスーパーコンピュータでも、ベクトル演算を効率的に処理するルーチンを一つ書くだけでよいのです。

RISC-Vの台頭

RISC-Vの支持者はみるみるうちに広がり、2019年12月、2,000人のエンジニアおよびその他の専門家が、カリフォルニア州サンノゼで開催されたRISC-Vサミットに参加しました。主にカルフォルニア大学バークリー校のコンピュータ科学者で構成されたRISC-Vファウンデーションのリーダーたちは、RISC-VベースのチップはARMだけではなくIntelをも追い越しうる成長性を秘めている、と主張しています。

RISC-Vは、2010年にカリフォルニア大学バークレー校のPar Labプロジェクトとして開始されました。これは、シンプルで効率的で拡張可能で、他のユーザーとの共有に制約のないISAを開発することをその目的としていました。そのため、Krste Asanovic(SiFiveの創設者)、Andrew Waterman、Yunsup Lee、およびDavid PattersonがRISC-Vを開発しました。彼らは2011年に最初のチップを製造し、仕様をオープンソースとして公開、商業製品にも利用しやすいBSDライセンス(オープンソースソフトウェアに適用されるライセンス体系の一種で、カリフォルニア大学バークリー校で生まれたBSD系UNIXのライセンスのために成立した方式)のもとで誰でも自由に使えるようにしました。試行錯誤の末、GitHubで公開されています。

Patterson(元カリフォルニア大学バークレー校コンピューターサイエンス教授および現在のGoogleのDistinguished Engineer)は、当初の動機は、チップのトランジスタ数が2年ごとに2倍になるという予測であるムーアの法則が減速しているため、チップ設計で実験を実行することであり「3カ月のプロジェクトとして開始したが、実際には4年を要した」と語っています。

「なぜ命令セットがだけオープンソース化しないのか?」

アカデミックグループは、Linuxがソフトウェアで達成し、ソフトウェアのあらゆる領域に広がった「オープンソース」に触発されました。彼らは、プレゼンテーションの序盤に必ず「なぜ、ハードウェアだけがオープンソース化しないのか?」と語りかけるスライドを配置します。

しかし、オープンソースはハードウェアにはそのまま移植できる概念ではありませんでした。アカデミアのチームは、Intel、ARMらのプロプライエタリ(専売的)なエコシステムのせいで、研究のための安価なライセンスを取得することができない、と理解したとき、独自のアーキテクチャを創造する決断を下したのです。彼らはLinuxがソフトウェアに対して行ったことをハードウェアに対して実行しようと決心しました。

RISC-Vの開発チームの1人、Pattersonは、1980年代および1990年代のマイクロプロセッサ戦争の伝説的な人物です。彼はRISC(縮小命令セットコンピューティング)の共同発明者であり、CISC(複雑な命令セットコンピューティング)に反対しました。 ARM、Sun Microsystems、Mips(Pattersonのコンピューターサイエンスの定番教科書の共著者であり、スタンフォード大学の前学長ジョン・ヘネシーが起業)のような企業はRISCを支持し、IntelはCISCに焦点を当てました。IntelがPC戦争で勝利した一方で、RISCを採用するARMはスマートフォンを支配しました。現在、パターソンと彼の仲間のバークレーの研究者は、ARMの地位を揺るがす戦いの火蓋を切ったのです。

Pattersonは「うまくいくとすれば、RISC-VとNVIDIAだけでなく、人々が自分で設計し、コミュニティが利用できるようにしたり、改良したりできるコンピューティング機器の別の側面も見られるはずです」と語っています。

ドメイン固有アーキテクチャ(DSA)またはドメイン固有アクセラレータが今後の道である場合、人々がアクセラレータを追加できる設計が必要になります。RISC-Vは、オープンアーキテクチャであり、そのために設計されているため、非常に簡単にそれを実行できる、と彼は想定しています。パターソンがRISC-Vに賭ける理由は、彼が、ムーアの法則以降の世界において、DSAが次の道だと提唱していることと関係しているのです。

さらに、Intelは、製造の進歩だけではムーアの法則のペースを維持するのが難しいと感じているかもしれません。そのため、設計者はアプリケーション固有のプロセッサを作成して速度の低下を補うようにプレッシャーを受けている、というのがパターソンの持論です。パターソンとヘネシーが手掛けるコンピュータアーキテクチャの定番教科書の最新版である"Computer Architecture 6th Edition A Quantitative Approach" では、第7章にドメイン固有アーキテクチャ(DSA)の章が新設されています。

PattersonはRISC-Vの設計思想について、RISC-V原典の第1章でこう指摘しています。「ムーアの法則が通用しなくなったときにコスト・パフォーマンスを大きく向上させる唯一の道は、特定のドメイン向け命令を追加することである。例えばディープ・ラーニング、拡張現実、組み合せ最適化、グラフィックスなどのドメインが考えられる。つまり今日のISAにとって、オペコードの拡張の余地を予め確保しておくことが重要になっている」

コンピュータアーキテクチャの研究者は数十年もこのアイデアの周りで侃々諤々の議論を繰り広げてきましたが、ついに2015年に独立した非営利団体として「RISC-Vファウンデーション」を創設しました。

2016年、NvidiaはRISC-Vをグラフィック処理ユニット(GPU)のコントローラーとして使用すると発表しました。Nvidiaは現在、これらのチップを何百万個も出荷しています。そうは言っても、このようなチップでは、RISC-Vは組み込み制御プロセッサとして小さなタスクを処理する可能性が高いのですが、デバイスは依然としてメインプロセッサとしてARMデザインを使用しています。2017年、Western Digitalは、製品ライン全体をRISC-Vに移行すると発表し、コアをオープンソース化しました。

以前は、チップ設計者は、チップを製造するベンダーを選択する必要がありました。 RISC-Vを使用すると、RISC-Vを選択して、すべてのベンダーがビジネスを競います。許可を得ずに独自の拡張機能を追加できます。それは、まるでアプリケーションを開発するかのようです。そう彼らはまさしく「パンドラの箱」を開けようとしているのです。

なぜRISC−Vが注目を集めているか?

RISC-Vが多くの関心を集めている理由はいくつかあります。1つは、RISC-Vはオープンソースであり、ライセンス料を支払うことなく、誰でもISAを実装するプロセッサを設計できることを意味します。これにより、ISAは、時間の経過とともにアーキテクチャを確認、修正、および強化できる巨大な世界規模のデザインコミュニティに開かれます。しかし、ISAのみがオープンソースであるため、開発者はハードウェアデザインの知的財産を保護し、商用目的のために独自に所有することができます。

RISC-Vが業界の関心を集めた2番目の理由は、ISAが長期の実行可能性に対して安定であると同時に、幅広いアプリケーションに適応するようにカスタマイズできるように設計されていることです。ISAのコア仕様は、今後数か月で200人以上のRISC-V ファウンデーションのメンバーによる最終承認が予定されており、現在準拠しているプロセッサ向けに開発されたソフトウェアは、今から数年後に開発された同等のプロセッサ上で実行されるように凍結されます。ISAは、32ビット、64ビット、および128ビットの実装用に定義されており、より大きなベースの実装で実行可能なより小さなビット幅のコードを備えています。

ISAの基本仕様を補完するのは標準の拡張機能であり、多くは凍結され、最終承認に向けて順調に進んでいます。開発者は、アプリケーションの要求に応じて、これらの標準拡張を実装するかどうかを、基本実装で動作するように作成されたソフトウェアに悪影響を与えることなく実装できます。さらに、RISC-V開発者は、カスタマイズされた拡張機能を追加して設計をさらに最適化し、それがベースソフトウェアまたはツールへの悪影響をおよぼすことは、ほとんど確認されていません。

この標準ベースのカスタマイズ可能性のキメラは、業界の大きな関心を集めていますが、ISAのオープンソースの性質は、これを支援するエンジニアリングの盛況を助長しました。Linuxの基本ポート、GNUベースの開発ツール、およびいくつかのコアデザインは、オープンソースコミュニティからすでに入手可能です。

さらに、SiFive、NXP、Kendryte、GreenWaves Technologiesなどの企業は、市販のRISC-Vチップを作成しました。NvidiaやWestern Digitalのような他の企業は、内部使用向けのプロセッサの開発に、RISC-Vを採用し始めています。商用ソフトウェアの開発も進行中であり、Adacoreは、安全性とセキュリティが重要なアプリケーションのために、AdaおよびSparcプログラミング言語をRISC-Vに導入するよう取り組んでいます。

RISC-Vの支援者は世界中にいます。たとえば、中国ではRISC-Vの勢いが増しており、インドでは新興企業のInCoreがRISC-VプロセッサとAIアクセラレータに取り組んでいます。さらに、EE Times Indiaのレポートによると、RISC-Vはインドの国家ISAとして採用されており、同国の設計産業がIntel x86およびARM ISAに依存しないよう支援しています。ヨーロッパのエンベデッドワールドショーの訪問者は、RISC-Vの展示を楽しみました。

現在、RISC-Vファウンデーションに参加する企業・団体・教育機関にはGoogleやNVIDIA、サムスン電子、テスラ、TSMC、アリババ、ウエスタンデジタルといった大手企業を含んでおり、高価なプロプライエタリのライセンスに手が届かない新興国を含んだ世界各国との連携が開始されているのです。

市場予測: RISC-V CPUの出荷 CAGR146.2%

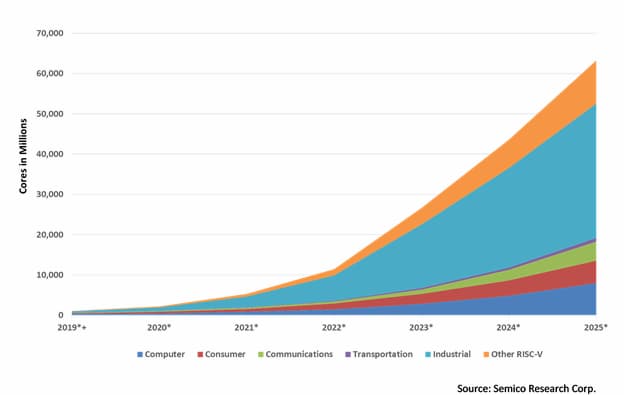

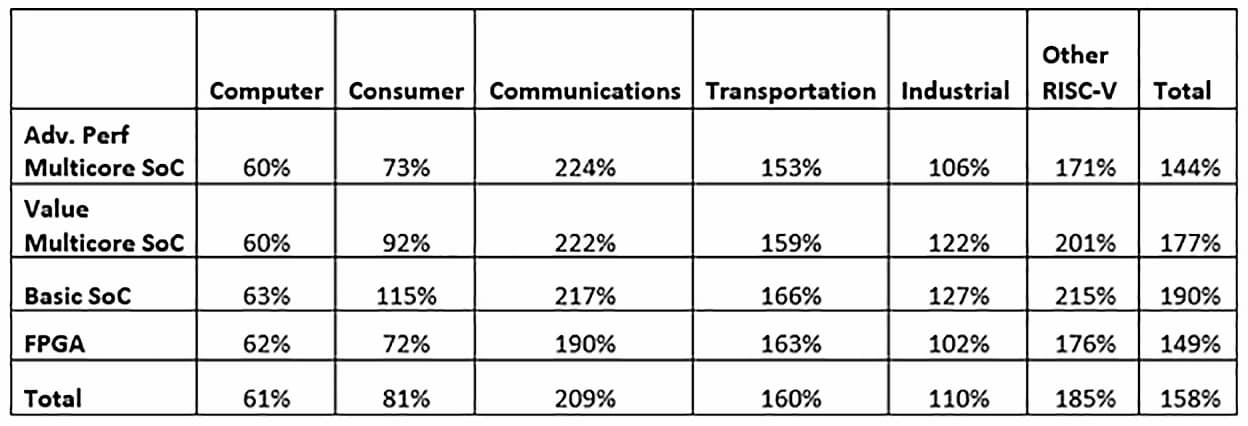

Semico Researchのマーケットリサーチ報告書 "RISC-V Market Analysis: The New Kid on the Block" は、2025年までに合計624億個のRISC-V CPUコアが市場で消費され、産業部門は167億個のコアが出荷される最大のセグメントになると予測しています(図1)。Semicoは、コンピューター、消費者、通信、輸送、および産業市場を含むセグメントは、2018年から2025年の間に146.2%の年間平均成長率(CAGR)を実現すると予想しています。Semicoは、RISC-Vが高性能マルチコアSoC、バリューマルチコアSoC、基本SoCおよびFPGAの4つの分野すべてで出荷を拡大すると予測しています。

2018年から2025年までのRISC-V CPUコアのCAGRの予測では、Semicoは、5Gの導入と5Gの採用により可能になる多数の製品およびアプリケーションにより、通信セクターが最大のCAGRを獲得すると予測しています(下図)。

自動車業界では、電動化への注目が高まり、安全性、車内体験、運転者支援、無線通信のためのCPUベースのシステムの採用が増えているため、輸送はCAGRで2番目に速いと推定されます。Semicoは、組織・企業がさまざまな性能および応用手段にわたってRISC-Vを設計しているだけでなく、SoCのコア数では、1コアから1000コア以上までの非常に幅広い使用のCPUを設計していることを発見しました。

このような予測が秘める特性のひとつは、自己成就的であることです。予測がコミュニティに浸透すると、コミュニティは予測を「達成」するためのスケジュールを組むため、予測が達成されるのです。

ARMがカスタム命令許可

イギリスのケンブリッジに本拠を置くARMは数十年前から存在し、そのアーキテクチャ設計はスマートフォンからサーバーに至るまですべてに使用されています。顧客はこれまでに1500億個以上のチップを出荷しており、ペースは加速しています。同社は今後2年間で500億個のチップの出荷を目標にしています。

ARMなどのISAの所有者は、断片化につながる可能性があるため、RISC-Vが許容するようなカスタマイズを許可するように動機付けられていません。ARMは数十年にわたって同社のISAを厳密に管理してきました。しかし、2019年10月、RISC-V ISAの台頭とそのユーザーコンフィギュアビリティ(ユーザーによる設定が可能であること)を受け、ARMは独自のカスタム命令を作ることを許可しました。これはRISC-Vの台頭を牽制する意味合いがあります。

ARMの顧客には不満があります。ARMとの契約内容は、ますます複雑化し、ライセンス料も上昇しています。ARMのビジネスモデルは、アーキテクチャ設計のためのライセンス料を前払いし、半導体チップの出荷数量に応じてロイヤリティー料を支払います。また、顧客がSoCを設計し市場投入するまでの期間が短くなっており、ARMの契約とビジネスプロセスは、柔軟性が欠けていると一部のプレイヤーからは考えられているようです。RISC-Vの表現する柔軟性、簡易さはこの点で対照をなしており、中国のベンダーなどはRISC-Vへのベットを増やしています。

RISC-Vの「IPの民主化」というゲームは、ARMのプロプライエタリなビジネスモデルに疑問を投げかけています。ARMはビジネスモデルの転換が迫られています。

Special thanks to supporters !

Shogo Otani, 林祐輔, 鈴木卓也, Mayumi Nakamura, Kinoco, Masatoshi Yokota, Yohei Onishi, Tomochika Hara, 秋元 善次, Satoshi Takeda, Ken Manabe, Yasuhiro Hatabe, 4383, lostworld, ogawaa1218, txpyr12, shimon8470, tokyo_h, kkawakami, nakamatchy, wslash, TS, ikebukurou.

月額制サポーター

Axionは吉田が2年無給で、1年が高校生アルバイトの賃金で進めている「慈善活動」です。有料購読型アプリへと成長するプランがあります。コーヒー代のご支援をお願いします。個人で投資を検討の方はTwitter(@taxiyoshida)までご連絡ください。

投げ銭

投げ銭はこちらから。金額を入力してお好きな額をサポートしてください。

https://paypal.me/axionyoshi?locale.x=ja_JP

参考文献

- David Patterson. "Instruction Sets Want To Be Free: A Case for RISC-V". Youtube Video, Nov, 2015.

- Chris Mellor. WD to move all its stuff to RISC-V processors, build some kind of super data-wrangling stack. 1 Dec 2017. The Register.

- デイビッド・パターソン/アンドリュー・ウォーターマン/成田 光彰(訳). RISC-V 原典. 日経BP社. 2018年.

- Kevin Krewell. ARMがカスタム命令に対応、「Cortex-M33」から. 2019年10月17日. EE Times Japan,

- ジョン・ヘネシー.コンピュータアーキテクチャ[第6版]定量的アプローチ.Sep, 2019.

- デイビッド・パターソン.RISC-V原典 オープンアーキテクチャのススメ.Oct, 2018.

- "David Patterson. UC Berkeley’s David A. Patterson Sees the Future After Moore’s Law" Heppo Reads Staff.

- Richard Florida, Martin Kenney. The Globalization of Japanese R&D: The Economic Geography of Japanese R&D Investment in the United States. Economic Geography Vol. 70, No. 4 (Oct., 1994), pp. 344-369.

- Simone Ferriani et al. "THE INTELLECTUAL PROPERTY BUSINESS MODEL (IP-BM)" University Cambridge, Center for Technology Management.

- 西嶋 貴史. 「半導体 IP ライセンスで普及した ARM アーキテクチャ」. コンピュータ産業研究会2006年2月16日.